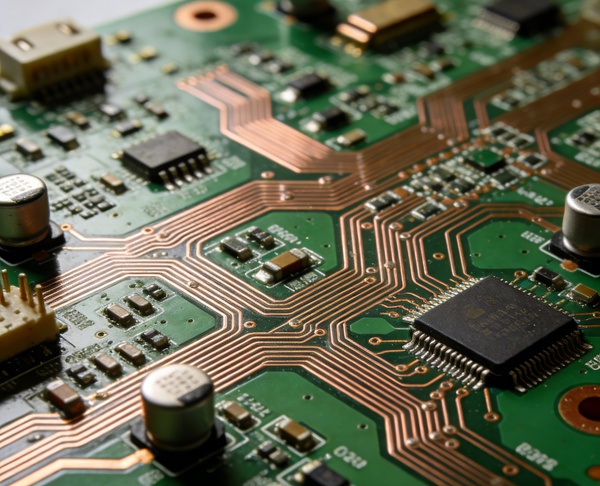

As data rates push into the multi-gigabit range (think DDR5, PCIe Gen6, and 112G SerDes), a PCB trace can no longer be treated as a simple wire. It is a transmission line. At high frequencies, the physical geometry of your board directly dictates the electrical performance.

In this guide, we’ll move beyond “basic routing” to explore the advanced physics of Signal Integrity (SI) and how to ensure your High Frequency PCB functions correctly on the first spin.

1. The Foundation: Stack-up and Impedance Control

High-speed design starts with the substrate, not the traces. If your layer stack-up is poorly planned, no amount of “pretty routing” will save the signal.

- Reference Planes are Non-Negotiable: Every high-speed signal must have a continuous, unbroken reference plane (Ground or Power) directly adjacent to it. This minimizes the Loop Inductance.

- Controlled Impedance: Most high-speed interfaces require specific impedance (typically $50\Omega$ single-ended or $90\Omega/100\Omega$ differential).

- Expert Tip: Work with your PCB Manufacturing partner before you start routing. Ask for their stack-up calculator results based on their specific FR4 or Rogers materials.

2. Advanced Routing Tactics

Differential Pair Routing

Differential signaling (like USB 3.0 or HDMI) relies on the rejection of common-mode noise.

- Maintain Symmetry: The two traces must be of equal length (within mils) and constant spacing.

- The “Tight Coupling” Myth: While coupling is good, maintaining a constant distance to the reference plane is more critical for impedance stability than the distance between the two traces themselves.

Via Management: The Hidden Capacitance

Vias are “speed bumps” for high-speed signals. They introduce parasitic capacitance and inductance.

- Minimize Via Count: Ideally, high-speed signals should stay on one layer.

- Back-Drilling: For ultra-high-speed designs (25Gbps+), the unused “stub” of a via can act as a resonator, destroying the signal. Back-drilling is the professional solution to remove these stubs.

- Related: Learn how HDI-PCB technology uses microvias to eliminate stubs and save space.

5 Steps to Professional High-Speed Routing

Target: Hardware Engineers & PCB Designers

Focus: Minimizing Signal Degradation

- Step 1: Pre-Layout Simulation

Use tools like HyperLynx or Altium’s SI engine to define your constraints. Know your Critical Length—the length at which a trace must be treated as a transmission line.

- Step 2: Component Placement for Shortest Paths

Place high-speed ICs (CPU, FPGA) and their associated memory (DDR) as close as possible. Orient them to minimize “crossovers” in the address and data buses.

- Step 3: Route the “Victims” and “Aggressors”

Route the most sensitive high-speed signals first. Use the 3W Rule (spacing between traces should be 3x the trace width) to reduce Crosstalk.

- Step 4: Length Matching (Tuning)

Use serpentine routing to match the lengths of signals within a bus (like DDR).

Pro Tip: Don’t just match the total length; match the “flight time.” Account for the different signal speeds on internal vs. external layers (Stripline vs. Microstrip). - Step 5: Post-Layout DRC & Eye Diagram Check

If possible, run a post-layout simulation to view the Eye Diagram. A “wide open eye” indicates a clean signal with low jitter and noise.

3. Managing EMI (Electromagnetic Interference)

High-speed boards are effectively antennas. To prevent your board from failing EMC certification:

- Avoid Split Planes: Never route a high-speed signal over a gap in the reference plane. This creates a massive EMI loop.

- Stitch Vias: Use “Ground Stitching Vias” around the board edge and near high-speed via transitions to provide a low-impedance return path.

- Material Choice: For 10GHz+ applications, standard FR4 may be too “lossy.” Consider Ceramic PCB or high-frequency laminates like Rogers 4350B.

4. Why Fabrication Precision Matters

A 1-mil variation in trace width might not matter for a toy, but in a Rigid PCB running a 10Gbps signal, it can cause a significant impedance shift.

At Hansphere, we use laser-direct imaging (LDI) and advanced AOI (Automated Optical Inspection) to ensure that the physical traces exactly match your digital design. This precision is vital for PCB Assembly of BGA components with 0.4mm pitch.

FAQ – High-Speed PCB Layout and Routing

A: Microstrip is on the outer layer (faster, but more EMI). Stripline is sandwiched between two ground planes (slower, but better shielded and more consistent impedance).

A: Use teardrops at the junction of traces and pads/vias. They reduce mechanical stress and help maintain a more gradual impedance transition, especially in Flexible PCBs.

A: Never use them. 90-degree corners cause a change in trace width at the vertex, leading to impedance discontinuity. Always use 45-degree bends or rounded corners.

Conclusion

High-speed PCB design is about controlling the environment through which electrons flow. By mastering stack-up, respecting return paths, and utilizing advanced manufacturing techniques, you can ensure your most complex designs operate with rock-solid stability.

Building a High-Speed Masterpiece? Don’t leave your signal integrity to chance. Hansphere’s Engineering Team provides full DFM reviews for high-speed layouts. Contact us today to discuss your project specifications.