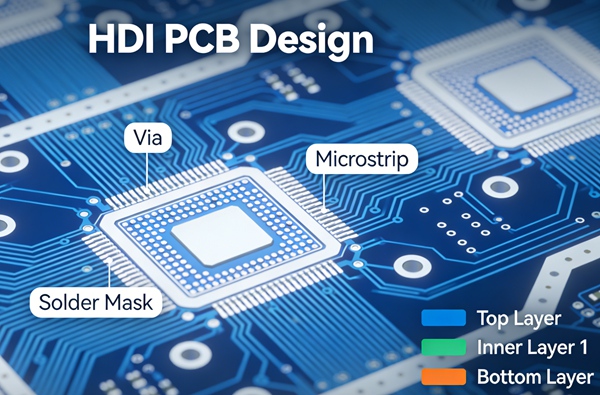

Die HDI-Leiterplattentechnologie ermöglicht elektronische Designs mit hoher Dichte und hoher Leistung, aber sie führt auch zu einzigartigen Fehlermechanismen, die bei Standard-Leiterplatten nicht üblich sind. Das Verständnis dieser Fehlermöglichkeiten ist entscheidend für die Verbesserung der Zuverlässigkeit und die Vermeidung kostspieliger Ausfälle im Feld.

Dieser Artikel behandelt HDI-LEITERPLATTE Fehleranalyse und Zuverlässigkeitsrisiken, und bietet Ingenieuren einen praktischen Einblick in Ursachen, Erkennungsmethoden und Präventionsstrategien.

🔗 Teil der HDI PCB Design Serie

HDI PCB Design: Technologie, Stackup, Weiterleitung, und Herstellung

Warum HDI-Leiterplatten anders ausfallen

HDI-Leiterplatten sind aus folgenden Gründen empfindlicher:

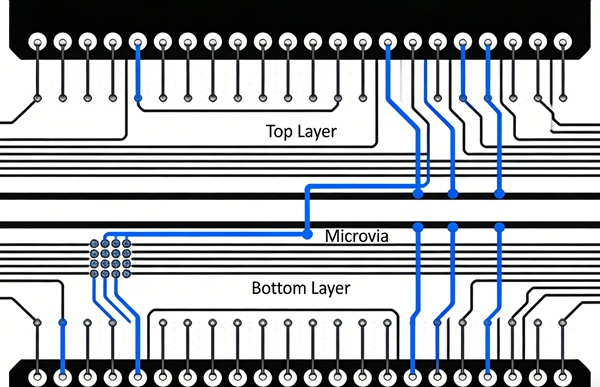

- Microvia-Strukturen

- Mehrere Laminierschnittstellen

- Dünne dielektrische Schichten

- Feindrähte

Diese Faktoren verstärken die Auswirkungen von Design- und Prozessvariationen.

Häufige HDI PCB-Fehlermodi

Microvia-Rissbildung

Verursacht durch:

- Thermisches Zyklieren

- Schlecht über Füllung

- CTE-Fehlanpassung

Microvia-Rissbildung führt häufig zu intermittierenden Ausfällen.

Delamination an der Grenzfläche

Findet statt bei:

- Schnittstellen für die Laminierung

- Kupfer-Harz-Grenzen

Ausgelöst durch thermische Belastung und schlechte Materialverträglichkeit.

Lücken in der Beschichtung und unvollständige Füllung

Ergebnisse aus:

- Unzureichend über die Füllung

- Schlechte Kontrolle der Beschichtung

Diese Mängel beeinträchtigen die mechanische und elektrische Zuverlässigkeit.

Spurenüberätzung und Öffnungen

Feine Linien erhöhen die Anfälligkeit für:

- Über-Ätzen

- Prozessdrift

Dies führt zu offenen Stromkreisen bei thermischer oder mechanischer Belastung.

Fehleranalysetechniken für HDI-PCBs

Querschnittsanalyse

- deckt Microvia und Laminierungsfehler auf

- Unverzichtbar für die Identifizierung der Grundursache

Röntgeninspektion

- Erkennt Hohlräume und Ausrichtungsfehler

- Zerstörungsfrei

Thermische Zyklustests

- Simuliert die Betriebsbelastung

- Deckt ermüdungsbedingte Ausfälle auf

Konstruktionsbedingte Zuverlässigkeitsrisiken

Mangelnde Zuverlässigkeit hat häufig folgende Ursachen:

- Übermäßig viele gestapelte Mikrovias

- Aggressive Mindestvorschriften

- Unzureichende Strom-/Bodenstrukturen

🔗 Einfluss auf das Design:

HDI PCB Routing-Regeln und BGA Fanout-Techniken

Fertigungsbedingte Zuverlässigkeitsrisiken

Gemeinsame Mitarbeiter in der Produktion:

- Prozessvariabilität

- Unzureichende Kontrolle

- Nicht validierte Materialien

🔗 Auswirkungen auf die Produktion:

HDI PCB-Herstellungsprozess und Optimierung der Ausbeute

Vorbeugende Design-Strategien

Um HDI-Ausfälle zu reduzieren:

- Begrenzung gestapelter Mikrovias

- Verwendung bewährter Materialien

- Möglichst konservativ gestalten

- Validierung mit Pilot-Builds

Zuverlässigkeitsprüfung und Qualifizierung

Zu den empfohlenen Tests gehören:

- Thermisches Zyklieren

- Mechanische Belastungstests

- Umweltexposition

Die Tests sollten den realen Bedingungen entsprechen.

Zusammenfassung bewährter Praktiken

- Verständnis der HDI-spezifischen Ausfallmechanismen

- Berücksichtigung der Zuverlässigkeit während der Entwicklung - nicht danach

- Enge Zusammenarbeit mit Herstellern

- Überprüfung der Entwürfe durch robuste Tests

Schlussfolgerung

Die Zuverlässigkeit von HDI-Leiterplatten hängt von einem tiefen Verständnis der Fehlermechanismen und disziplinierten Entwurfs- und Fertigungsverfahren ab. Durch den proaktiven Umgang mit Zuverlässigkeitsrisiken können Ingenieure die Vorteile der HDI-Technologie voll ausschöpfen und gleichzeitig Ausfälle im Feld minimieren.

Dieser Artikel vervollständigt die HDI PCB Design Inhaltscluster mit einem starken Schwerpunkt auf der Zuverlässigkeit in der Praxis.

FAQ - HDI PCB-Fehleranalyse

A: Microvia-Risse, die durch thermische Spannungen verursacht werden.

A: Nicht von Natur aus; die Zuverlässigkeit hängt von der Design- und Prozessqualität ab.

A: Oft nicht; es ist eine Röntgen- oder Querschnittsanalyse erforderlich.

A: Durch die Verwendung konservativer Regeln und geprüfter Materialien.

A: Ja, insbesondere ohne strenge Prozesskontrolle.

A: Vor der Serienproduktion, während der Pilotproduktion.