Das Design von Hochgeschwindigkeits-Leiterplatten ist zu einer grundlegenden Anforderung in der modernen Elektronik geworden. Da die Datenraten steigen und die Spannungsspannen schrumpfen, reichen herkömmliche PCB-Designansätze nicht mehr aus, um eine zuverlässige Systemleistung zu gewährleisten.

Diese Säule bietet einen strukturierten Überblick über Hochgeschwindigkeits-PCB-Design, in dem die wichtigsten Herausforderungen in Bezug auf Signalintegrität, Layout-Strategie, Stromversorgung und Herstellbarkeit behandelt werden. Jeder Abschnitt verlinkt zu ausführlichen technischen Artikeln, die sich detailliert mit spezifischen Designüberlegungen befassen.

Was macht eine Hochgeschwindigkeitsleiterplatte aus?

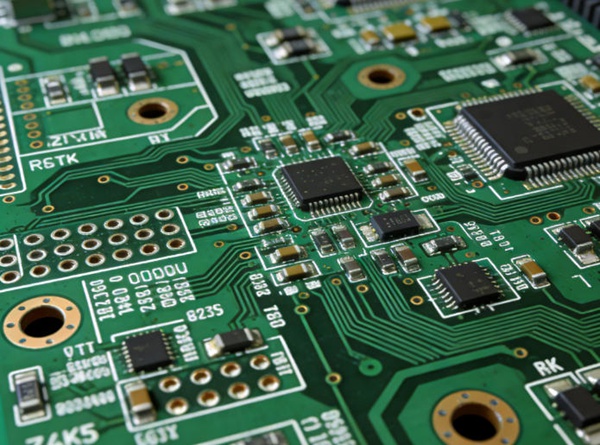

Eine Leiterplatte wird im Allgemeinen als “Hochgeschwindigkeitsleiterplatte” bezeichnet, wenn die Signalanstiegszeiten so kurz sind, dass sich die Verbindungen wie Übertragungsleitungen verhalten. Bei diesen Designs wirken sich Leiterbahngeometrie, Referenzebenen, Durchkontaktierungen und Stackup-Entscheidungen direkt auf das Signalverhalten aus.

Zu den gemeinsamen Merkmalen von Hochgeschwindigkeits-Leiterplattenentwürfen gehören:

- Kontrolliertes Impedanz-Routing

- Strenge Anforderungen an Timing und Versatz

- Empfindlichkeit gegenüber Nebensprechen und EMI

- Starke Abhängigkeit von Stapel- und Bezugsebenen

Das Verständnis dieser Grundlagen ist unerlässlich, bevor man sich mit Layout- oder Routing-Techniken befasst.

Herausforderungen an die Signalintegrität beim Hochgeschwindigkeits-Leiterplattenentwurf

Die Signalintegrität ist bei Hochgeschwindigkeitsdesigns oft das Hauptanliegen. Schlecht verwaltete Impedanzen, Diskontinuitäten und Rückleitungen können zu Reflexionen, Timing-Fehlern und einer Verschlechterung des Augendiagramms führen.

Zu den wichtigsten SI-Herausforderungen gehören:

- Impedanzdiskontinuitäten durch Durchkontaktierungen und Schichtübergänge

- Nebensprechen zwischen benachbarten Hochgeschwindigkeitssignalen

- Überlegungen aufgrund einer unsachgemäßen Beendigung

- Rückwegunterbrechungen über Bezugsebenen

Für ein effektives Hochgeschwindigkeits-Leiterplattendesign müssen diese Probleme bereits in der Layout-Phase angegangen werden.

🔗 Eingehende Analyse:

Signalintegrität im Hochgeschwindigkeits-PCB-Design: Analyse und häufige Fallstricke

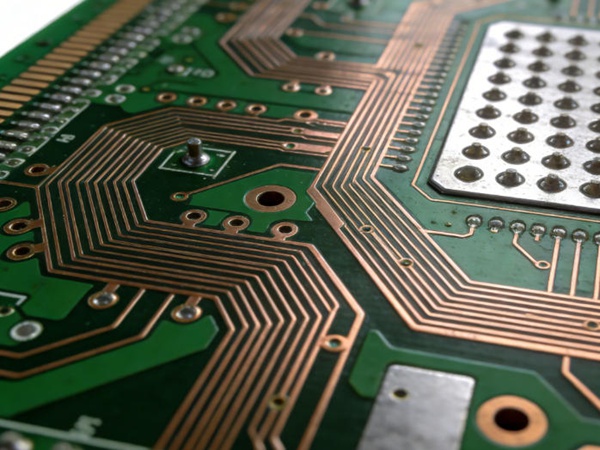

Layout- und Routing-Strategien für Hochgeschwindigkeitsplatinen

Layout- und Routing-Entscheidungen spielen eine entscheidende Rolle bei der Bestimmung der Signalqualität. Bei Hochgeschwindigkeits-Leiterplatten sind die Platzierung und das Routing eng mit der elektrischen Leistung verbunden.

Zu den bewährten Verfahren gehören häufig:

- Kurzes und direktes Routing für kritische Signale

- Konsistente Bezugsebenen für Rückströme

- Kontrollierte differentielle Paarführung

- Sorgfältige Via-Nutzung und Ebenenübergänge

Diese Techniken tragen dazu bei, die Signalverschlechterung und die zeitliche Unsicherheit zu minimieren.

🔗 Technischer Leitfaden:

Best Practices für High-Speed PCB-Layout und Routing

Leistungsintegrität im Hochgeschwindigkeits-PCB-Design

Mit zunehmenden Schaltgeschwindigkeiten wird die Stromversorgungsintegrität ebenso wichtig wie die Signalintegrität. Ein schlechtes PDN-Design kann zu Spannungsrauschen führen, das sich direkt auf das Signaltiming und die Zuverlässigkeit auswirkt.

Wichtige Überlegungen von PI sind:

- Entkopplung und Platzierung von Großkondensatoren

- Steuerung der Impedanz der Leistungsebene

- Wechselwirkung zwischen PDN-Rauschen und Hochgeschwindigkeitssignalen

Hochgeschwindigkeitsdesigns erfordern eine koordinierte SI- und PI-Planung, anstatt sie als separate Probleme zu behandeln.

🔗 Verwandtes Thema:

Herausforderungen an die Stromversorgungsintegrität bei der Entwicklung von Hochgeschwindigkeits-Leiterplatten

Überlegungen zu EMI und Nebensprechen

Hochgeschwindigkeitssignale sind eine häufige Quelle für elektromagnetische Störungen. Ohne entsprechende Kontrolle kann die EMI sowohl die Einhaltung von Vorschriften als auch die Systemleistung beeinträchtigen.

Zu den wichtigsten Minderungsstrategien gehören:

- Aufrechterhaltung kontinuierlicher Rücklaufwege

- Verwaltung von Flankenraten und Leiterbahnabständen

- Effiziente Nutzung von Bezugsebenen

- Minimierung der Schleifenbereiche

Crosstalk und EMI lassen sich am besten durch Layout-Disziplin und nicht durch späte Korrekturen beheben.

🔗 Ausführliche Diskussion:

EMI- und Crosstalk-Kontrolltechniken im Hochgeschwindigkeits-Leiterplattenentwurf

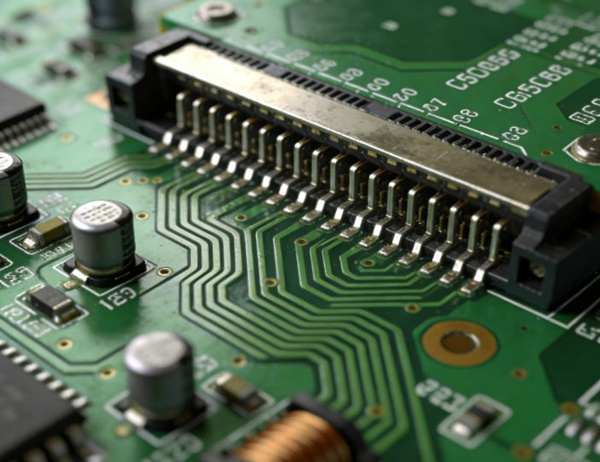

Fertigungs- und DFM-Herausforderungen bei Hochgeschwindigkeits-PCBs

Hochgeschwindigkeits-Leiterplattendesigns stoßen oft an die Grenzen der Fertigung und Montage. Leiterbahnbreitentoleranzen, Lagenregistrierung und Materialauswahl können sich alle auf die elektrische Leistung auswirken.

Zu den Überlegungen zur Herstellbarkeit gehören:

- Durchführbarkeit der Stapelung und Impedanztoleranz

- Über Strukturen und Bohrzwänge

- Materialbeschaffenheit und Verlustmerkmale

Bei den Konstruktionsentscheidungen muss ein Gleichgewicht zwischen elektrischer Leistung und realistischen Fertigungsmöglichkeiten gefunden werden.

🔗 Perspektive der Herstellung:

Hochgeschwindigkeits-PCB-Design für Herstellbarkeit und Ausbeute

Wie Ingenieure das High-Speed PCB Design angehen sollten

Erfolgreiches Hochgeschwindigkeits-Leiterplatten-Design erfordert eine Denkweise auf Systemebene. Ingenieure sollten:

- Definieren Sie geschwindigkeitskritische Signale frühzeitig

- Koordinierung von Stapelung, Layout und Routing-Entscheidungen

- Validierung von Entwürfen durch Simulation und Messung

- Enge Zusammenarbeit mit Herstellern

Hochgeschwindigkeits-Leiterplattendesign ist keine einzelne Technik, sondern ein disziplinierter Arbeitsablauf.

Schlussfolgerung

Das Design von Hochgeschwindigkeits-Leiterplatten stellt einzigartige Herausforderungen dar, die eine sorgfältige Beachtung der Signalintegrität, der Layoutstrategie, der Stromversorgung und der Herstellbarkeit erfordern. Durch das Verständnis der zugrunde liegenden Prinzipien und die konsequente Anwendung von Best Practices können Ingenieure zuverlässige Hochgeschwindigkeitssysteme entwickeln.

Diese Seite dient als zentrales Nachschlagewerk für Hochgeschwindigkeits-Leiterplattendesign-Themen mit detaillierten Artikeln, in denen jede Herausforderung eingehend untersucht wird.