Eine strukturierte Entwurfsprüfung ist eine der effektivsten Methoden, um kostspielige Re-Spins bei Hochgeschwindigkeits-Leiterplattenprojekten zu verhindern. Viele Fehler im Zusammenhang mit Signalintegrität, Stromversorgungsintegrität, EMI oder Fertigungsausbeute können durch die Anwendung einer disziplinierten Checkliste frühzeitig erkannt werden.

Diese Checkliste für die Überprüfung von Hochgeschwindigkeits-PCB-Designs bietet einen umfassenden, erfahrungsbasierten Rahmen zur Überprüfung von Hochgeschwindigkeits-Leiterplattenentwürfen vor der Fertigung.

1. Überprüfung von System und Architektur

- ⬜ Hochgeschwindigkeitsschnittstellen klar gekennzeichnet

- ⬜ Datenraten und Flankenraten definiert

- ⬜ Zeitliche Abstände dokumentiert

- ⬜ Leistungsbereiche und Spannungstoleranzen definiert

- ⬜ Berücksichtigte Umweltbedingungen (Temperatur, Lärm)

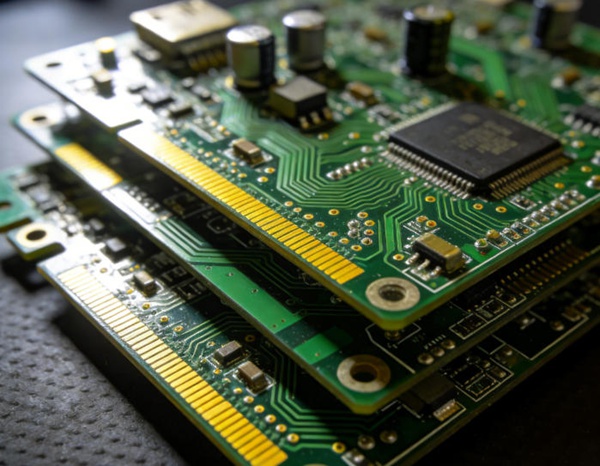

2. Stapelung und Materialprüfung

- ⬜ Stackup vom Leiterplattenhersteller geprüft und genehmigt

- ⬜ Symmetrische Stapelstruktur verwendet

- ⬜ Hochgeschwindigkeits-Signalebenen neben massiven Bezugsebenen

- ⬜ Dielektrische Dicke unterstützt die Zielimpedanz

- ⬜ Material Dk und Df entsprechend der Datenrate

- ⬜ Berücksichtigung von Glasgewebeeffekten bei Differentialpaaren

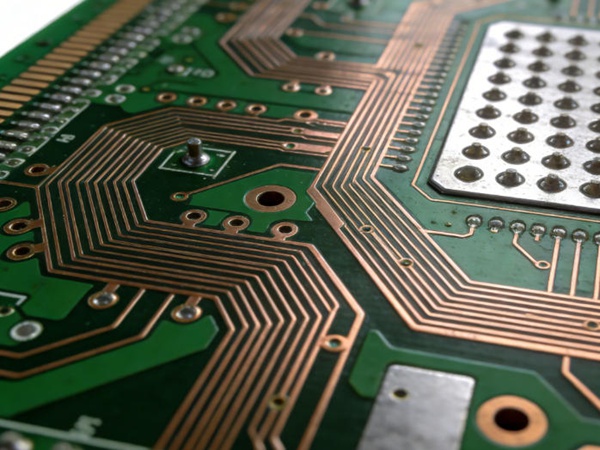

3. Überprüfung von Impedanz und Übertragungsleitung

- ⬜ Zielimpedanz für alle Hochgeschwindigkeitsnetze festgelegt

- Leiterbahnbreite und -abstände innerhalb der Fertigungstoleranz

- ⬜ Durchgängig schichtübergreifende Impedanzkontrolle

- ⬜ Minimale Impedanzdiskontinuitäten

- ⬜ Testkupons definiert, falls erforderlich

4. High-Speed Layout & Routing Überprüfung

- ⬜ Kritische Netze werden zuerst weitergeleitet

- ⬜ Hochgeschwindigkeitsbahnen in der Nähe von Bezugsebenen verlegt

- ⬜ Keine Leitweglenkung über Ebenenunterteilungen

- ⬜ Differentialpaare längenangepasst und symmetrisch gehalten

- Paralleles Routing zur Reduzierung des Übersprechens auf ein Minimum reduziert

- ⬜ Minimierung der Durchgangszahl in kritischen Netzen

🔗 Hinweis:

Best Practices für High-Speed PCB-Layout und Routing

5. Überprüfung von Rückweg und Referenzebene

- ⬜ Durchgängige Rückleitungen für alle Hochgeschwindigkeitssignale

- ⬜ Verwalten von Bezugsebenenübergängen mit Stitching Vias

- ⬜ Keine unterbrochenen Rückleitungen bei kritischen Signalen

- ⬜ Integrität der Grundplatte beibehalten

6. Überprüfung der Signalintegrität

- ⬜ SI-Risiken frühzeitig erkannt

- ⬜ Kontrollierte Reflexionen mit Abschluss, wo erforderlich

- ⬜ Übersprechen innerhalb akzeptabler Grenzen

- ⬜ Bewertung und ggf. Entschärfung von Abzweigungen

- ⬜ Überprüfung der Simulationsergebnisse (falls zutreffend)

🔗 Hinweis:

Signalintegrität im Hochgeschwindigkeits-PCB-Design

7. Überprüfung der Energieintegrität

- ⬜ Zielimpedanz für jede Stromschiene festgelegt

- ⬜ Angemessene Entkopplungshierarchie eingeführt

- ⬜ Kondensatoren in der Nähe der IC-Leistungsanschlüsse

- Niederinduktive Leistungs- und Erdungsebenen verwendet

- ⬜ Bewertung der PDN-Resonanzrisiken

🔗 Hinweis:

Leistungsintegrität im Hochgeschwindigkeits-PCB-Design

8. EMI / EMC Überprüfung

- ⬜ Minimierung der Schleifenbereiche

- ⬜ Kontrolle der Flankensteilheit, soweit möglich

- ⬜ Massive Masseflächen zur Abschirmung

- ⬜ E/A-Schnittstellen auf EMI-Risiko geprüft

- ⬜ EMI-Abschwächung an der Quelle geplant

🔗 Hinweis:

EMI- und EMC-Überlegungen beim Entwurf von Hochgeschwindigkeits-Leiterplatten

9. Überprüfung von Produktion und Ausbeute

- ⬜ Stapelung kompatibel mit den Fertigungsmöglichkeiten

- ⬜ Kontrollierte Impedanztoleranz realistisch

- ⬜ Über Größen und Seitenverhältnisse herstellbar

- ⬜ Fortschrittliche Materialien verfügbar und qualifiziert

- ⬜ Überprüfung der Montageauflagen

🔗 Hinweis:

Hochgeschwindigkeits-PCB-Design für Fertigung und Ausbeute

10. Überprüfung der Testbarkeit und Validierung

- ⬜ Inklusive Impedanz- und elektrische Prüfstrukturen

- ⬜ Sondenzugang für kritische Signale

- ⬜ Stromschienenmesspunkte vorhanden

- ⬜ Debug-Strategie festgelegt

Tor der Endkontrolle

- ⬜ Alle Punkte der Checkliste überprüft und genehmigt

- ⬜ Mit Plänen zur Risikominderung dokumentierte Risiken

- ⬜ Entwurf eingefroren für die Herstellung

Schlussfolgerung

Ein disziplinierter Entwurfsprüfungsprozess verringert das Risiko von Fehlern auf Hochgeschwindigkeits-Leiterplatten erheblich. Diese Checkliste fasst bewährte Verfahren in den Bereichen Signalintegrität, Stromversorgungsintegrität, EMI, Stackup-Design und Fertigung zusammen, um zuverlässige, skalierbare Hochgeschwindigkeitssysteme zu unterstützen.

Diese Checkliste dient als praktische technische Referenz sowohl für Entwurfsteams als auch für Prüfer.

FAQ - Überprüfung des Hochgeschwindigkeits-PCB-Designs

A: Vor der Fertigstellung des Layouts und noch einmal vor der Freigabe für die Fertigung.

A: Ja. Dies gilt im Großen und Ganzen für DDR-, PCIe-, USB-, Ethernet- und ähnliche Schnittstellen.

A: Nein. Sie ergänzt die Simulation, indem sie strukturelle und prozessbezogene Risiken erfasst.

A: Konstrukteure, SI/PI-Ingenieure, Fertigungspartner und Prüfingenieure.

A: Ja. Sie sollte je nach Projektkomplexität und Risikoniveau angepasst werden.