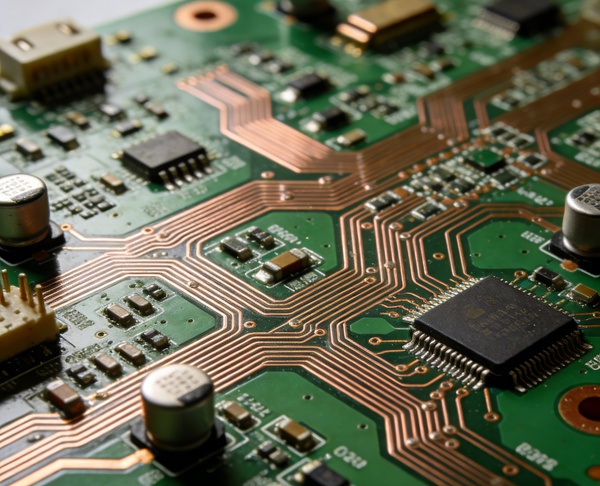

Mit Hochgeschwindigkeit PCB-Design, Layout- und Routing-Entscheidungen bestimmen direkt die Signalqualität. Da die Flankenraten steigen und die Timing-Spannen schrumpfen, können selbst kleine Layout-Entscheidungen - wie z. B. die Übergänge zwischen den Referenzebenen oder die Platzierung von Vias - zu erheblichen Problemen bei der Signalintegrität führen.

Dieser Artikel befasst sich mit praktische Best Practices für Layout und Routing von Hochgeschwindigkeits-Leiterplatten, und hilft Ingenieuren, Reflexionen, Übersprechen und EMI durch disziplinierte Entwurfstechniken zu minimieren.

🔗 Dieser Artikel ist Teil des Kernthemas:

Hochgeschwindigkeits-PCB-Design: Herausforderungen in Bezug auf Signalintegrität, Layout und Fertigung

Warum Layout und Routing bei High-Speed-Designs so wichtig sind

Bei hohen Geschwindigkeiten verhalten sich Leiterbahnen auf der Leiterplatte wie Übertragungsleitungen und nicht wie einfache Verbindungen. Das Signalverhalten wird durch die Geometrie der Leiterbahnen, Bezugsebenen, Durchkontaktierungen und die Routing-Topologie beeinflusst.

Schlechtes Layout und Routing können dazu führen:

- Impedanz-Diskontinuitäten

- Reflexionen und Klingeln

- Übermäßiges Nebensprechen

- Zeitversatz und Verschlechterung des Augendiagramms

Diese Probleme lassen sich im späteren Verlauf des Entwurfszyklus nur schwer beheben, weshalb eine frühzeitige Layout-Disziplin unerlässlich ist.

Bauteilplatzierung für Hochgeschwindigkeits-PCBs

Ein effektives High-Speed-Leiterplattenlayout beginnt mit einer durchdachten Platzierung der Komponenten.

Zu den wichtigsten Vermittlungsprinzipien gehören:

- Platzieren Sie Hochgeschwindigkeitskomponenten nahe beieinander, um die Länge der Leiterbahnen zu minimieren.

- Ausrichten von Komponenten zur Unterstützung direkter Routing-Pfade

- Kurze und vorhersehbare Signalwege für hohe Geschwindigkeiten

- Trennen Sie digitale Hochgeschwindigkeitsbereiche von empfindlichen analogen Bereichen

Die Platzierung sollte sich eher am Signalfluss als an der schematischen Hierarchie orientieren.

Grundlagen der kontrollierten Impedanzverlegung

Kontrolliertes Impedanz-Routing ist eine Grundlage für das Design von Hochgeschwindigkeits-Leiterplatten.

Zu den bewährten Praktiken gehören:

- Frühzeitige Festlegung von Impedanzzielen mit dem gewählten Stackup

- Konsistente Leiterbahnbreite und -abstände beibehalten

- Vermeiden Sie abrupte Änderungen der Geometrie

- Verwenden Sie Bezugsebenen direkt neben den Signalebenen

Jede Abweichung der Leiterbahngeometrie oder der Kontinuität der Bezugsebene führt zu Impedanzunterbrechungen, die die Signalqualität beeinträchtigen.

🔗 Verwandte Stiftung:

Signalintegrität im Hochgeschwindigkeits-PCB-Design

Bewährte Praktiken für das Differential Pair Routing

Differentialsignalisierung wird häufig in Hochgeschwindigkeitsschnittstellen wie PCIe, USB und Ethernet verwendet.

Zu den wichtigsten Leitlinien für die Streckenführung gehören:

- Anpassung der Leiterbahnlängen innerhalb definierter Toleranzen

- Einheitliche Paarabstände beibehalten

- Differentialpaare ohne Trennung zusammenführen

- Vermeiden Sie unnötige Via-Übergänge

Bei der Längenanpassung ist Vorsicht geboten, da eine Überkompensation mit Serpentinenverlegung zusätzliche Diskontinuitäten verursachen kann.

Via-Nutzung und Ebenenübergänge

Durchkontaktierungen sind eine häufige Quelle von Impedanzdiskontinuitäten in Hochgeschwindigkeitsleiterplatten.

Empfohlene Praktiken:

- Minimierung der Durchgangszahl bei kritischen Signalen

- Rückwärtsbohren bei Bedarf für Hochgeschwindigkeitsverbindungen

- Beibehaltung der Kontinuität der Bezugsebene bei Ebenenübergängen

- Vermeiden Sie Stümpfe wann immer möglich

Die Via-Strategie sollte mit dem Stackup-Design und den Fertigungsbeschränkungen abgestimmt werden.

🔗 Auswirkungen auf die Produktion:

Hochgeschwindigkeits-PCB-Design für Herstellbarkeit und Ausbeute

Verwaltung von Rückweg und Referenzebene

Hochgeschwindigkeitssignale folgen immer einem Rückweg. Störungen im Rückweg können unerwartete EMI und Signalverzerrungen verursachen.

Zu den bewährten Praktiken gehören:

- Weiterleitung von Hochgeschwindigkeitssignalen über kontinuierliche Referenzebenen

- Vermeiden Sie die Überquerung von Ebenenrissen oder Lücken

- Verwendung von Stitching Vias in der Nähe von Schichtübergängen

- Halten Sie die Rückkehrwege kurz und vorhersehbar

Die Integrität des Rückkanals wird oft übersehen, ist aber entscheidend für einen zuverlässigen Hochgeschwindigkeitsbetrieb.

Nebensprechen und Abstandsregelung

Mit zunehmender Leiterbahndichte wird das Übersprechen zu einem erheblichen Problem.

Zur Reduzierung des Übersprechens:

- Ausreichende Abstände zwischen parallelen Hochgeschwindigkeitsstrecken einhalten

- Vermeiden Sie lange parallele Routingläufe

- Erforderlichenfalls Abschirmung oder Schutzleiter verwenden

- Signale auf benachbarten Ebenen orthogonal leiten

Die Abstandsregeln sollten auf Simulationen und empirischen Leitlinien beruhen und nicht auf willkürlichen Werten.

🔗 EWI-Perspektive:

EMI- und Crosstalk-Kontrolltechniken im Hochgeschwindigkeits-Leiterplattenentwurf

Routing-Order und Design-Disziplin

Die Hochgeschwindigkeitsstreckenführung sollte einer klaren Prioritätenfolge folgen:

- Kritische Hochgeschwindigkeitssignale

- Differentialpaare

- Taktgeber und zeitabhängige Netze

- Verbleibende Digital- und Steuersignale

Wenn kritische Netze zuerst geroutet werden, lassen sich Kompromisse vermeiden und die Signalintegrität erhalten.

Validierung und Überprüfung vor der Fertigstellung

Vor der Fertigstellung des Layouts einer Hochgeschwindigkeitsleiterplatte:

- Überprüfung des Routings auf Impedanzkonsistenz

- Durchgängigkeit der Bezugsebene prüfen

- Validierung über Strukturen

- Gegebenenfalls Durchführung von SI-Simulationen

Eine frühzeitige Validierung verringert das Risiko kostspieliger Umgestaltungen.

Schlussfolgerung

Hochgeschwindigkeits-Leiterplattenlayout und -Routing erfordern disziplinierte Planung, sorgfältige Ausführung und ein umfassendes Verständnis des Signalverhaltens. Durch die Befolgung bewährter Best Practices - mit Schwerpunkt auf Impedanzkontrolle, Rückleitungen und Routing-Strategie - können Ingenieure die Signalintegrität und die allgemeine Systemzuverlässigkeit erheblich verbessern.

Dieser Artikel dient als praktische Referenz für Layout- und Routing-Entscheidungen in Hochgeschwindigkeits-Leiterplatten-Design-Workflows.

FAQ - Hochgeschwindigkeits-PCB-Layout und Routing

A: Eine Leiterbahn benötigt eine kontrollierte Impedanz, wenn ihre Länge im Verhältnis zur Signalanstiegszeit elektrisch signifikant wird, was bei digitalen Hochgeschwindigkeitsdesigns häufig der Fall ist.

A: Die Längenanpassung ist für viele Hochgeschwindigkeitsschnittstellen wichtig, aber eine übermäßige Serpentinenverlegung kann zusätzliche Impedanzdiskontinuitäten einführen. Die Anpassung sollte den Schnittstellenspezifikationen folgen.

A: Weniger Durchkontaktierungen sind immer vorzuziehen. Jedes Via führt zu Impedanzänderungen, daher sollten kritische Hochgeschwindigkeitsnetze so wenig Vias wie möglich verwenden.

A: Automatisches Routing kann bei weniger kritischen Signalen hilfreich sein, aber Hochgeschwindigkeitsnetze erfordern in der Regel manuelles Routing und Überprüfung, um die Signalintegrität zu gewährleisten.

A: Unterbrochene Rückleitungen vergrößern den Schleifenbereich, was zu EMI, Rauschen und Signalverzerrungen führt. Kontinuierliche Bezugsebenen sind unerlässlich.

A: Der Stackup bestimmt die Impedanz, die Nähe zur Referenzebene und das Verhalten der Vias. Routing-Entscheidungen müssen mit dem gewählten Stackup übereinstimmen.

A: Das Kreuzen von Bezugsebenensplits mit Hochgeschwindigkeitssignalen ist einer der häufigsten und schädlichsten Fehler.