Die Signalintegrität (SI) ist einer der kritischsten Aspekte bei der Entwicklung von Hochgeschwindigkeits-Leiterplatten. Da die Signalanstiegszeiten immer kürzer und die Datenraten immer höher werden, können selbst kleine Unregelmäßigkeiten in der Verbindung zu Reflexionen, Zeitfehlern und einer Verschlechterung des Augendiagramms führen.

Dieser Artikel bietet einen praktischen Überblick über Signalintegrität beim Entwurf von Hochgeschwindigkeits-Leiterplatten, Der Schwerpunkt liegt auf häufigen Herausforderungen, Grundursachen und Best Practices, die Ingenieure bei Layout, Routing und Validierung anwenden können.

🔗 Dieser Artikel ist Teil des Kernthemas:

Hochgeschwindigkeits-PCB-Design: Signalintegrität, Layout, und Herausforderungen bei der Herstellung

Was Signalintegrität bei Hochgeschwindigkeits-PCBs bedeutet

Signalintegrität bezieht sich auf die Fähigkeit eines elektrischen Signals, seine vorgesehene Form und sein Timing bei der Ausbreitung durch eine Leiterplattenverbindung beizubehalten.

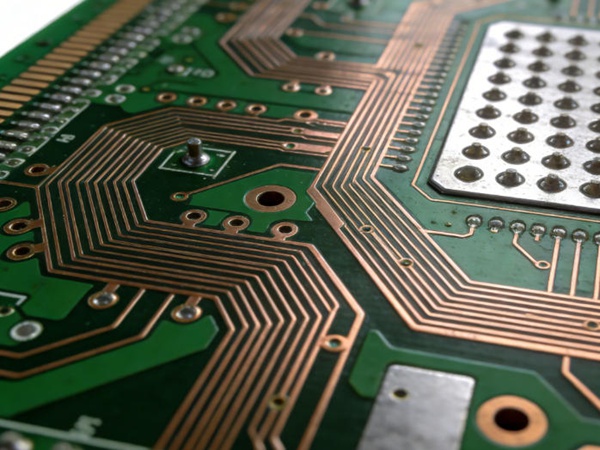

Bei Hochgeschwindigkeitsdesigns verhalten sich Leiterbahnen eher wie Übertragungsleitungen als wie ideale Drähte. Infolgedessen wird das Signalverhalten beeinflusst durch:

- Impedanz der Leiterbahn

- Bezugsebenen und Rückwege

- Durchkontaktierungen und Schichtübergänge

- Beendigung und Verladung

Probleme mit der Signalintegrität entstehen, wenn diese Elemente nicht sorgfältig kontrolliert werden.

Wenn die Signalintegrität zu einem Design-Problem wird

Probleme mit der Signalintegrität werden hauptsächlich verursacht durch Flankensteilheit, und nicht die Taktfrequenz. Ein Entwurf sollte als Hochgeschwindigkeitsentwurf behandelt werden, wenn die Leiterbahnlänge im Verhältnis zur Signalanstiegszeit elektrisch signifikant wird.

Zu den gängigen Indikatoren gehören:

- Schnelle Anstiegs-/Abfallzeiten

- Große Leiterbahnlängen

- Enge zeitliche Spielräume

- High-Density-Routing

Die Nichtbeachtung von SI-Überlegungen in dieser Phase führt häufig zu späten Umgestaltungen.

Häufige Probleme mit der Signalintegrität bei Hochgeschwindigkeits-PCBs

Reflexionen und Klingeln

Reflexionen treten auf, wenn entlang eines Signalwegs Impedanzfehlanpassungen bestehen. Diese Fehlanpassungen werden häufig verursacht durch:

- Über Übergänge

- Änderungen der Leiterbahnbreite

- Steckverbinder-Schnittstellen

- Unsachgemäße Beendigung

Reflexionen können Signalflanken verzerren und die Rauschspanne verringern.

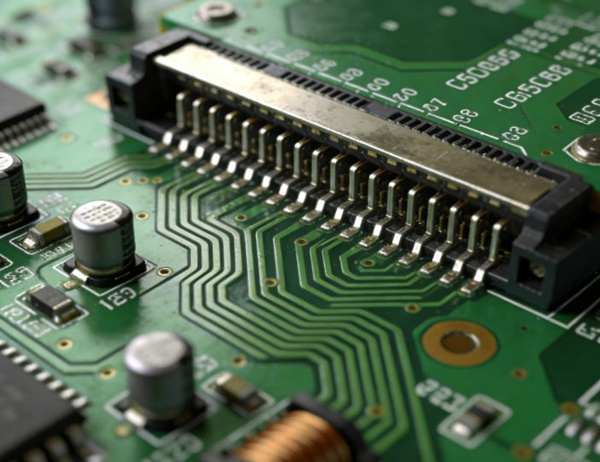

Nebensprechen zwischen benachbarten Signalen

Nebensprechen wird durch elektromagnetische Kopplung zwischen nahegelegenen Leiterbahnen verursacht. Es wird verstärkt, wenn Signale über große Entfernungen parallel verlaufen oder wenn die Abstände nicht ausreichen.

Übersprechen kann dazu führen:

- Zeitlicher Jitter

- Falsches Schalten

- Erhöhter Lärm

Um das Übersprechen zu kontrollieren, ist es wichtig, dass die Abstände und das Routing stimmen.

Unterbrechungen des Rückführungsweges

Hochgeschwindigkeitssignale erfordern immer einen kontinuierlichen Rückweg. Wenn Signale Ebenenunterteilungen oder Lücken überqueren, sind Rückströme gezwungen, einen Umweg zu machen, was die Schleifenfläche und das Rauschen erhöht.

Rückwegunterbrechungen sind eine wichtige, aber oft übersehene Quelle für SI- und EMI-Probleme.

🔗 Layout-Perspektive:

Best Practices für High-Speed PCB-Layout und Routing

Impedanzkontrolle und Übertragungsleitungseffekte

Ein kontrolliertes Impedanz-Routing ist für die Aufrechterhaltung der Signalintegrität von grundlegender Bedeutung.

Zu den wichtigsten Überlegungen gehören:

- Auswahl einer geeigneten Leiterbahngeometrie auf der Grundlage der Stapelung

- Konsistente Leiterbahnbreite und -abstände beibehalten

- Vermeidung von abrupten Geometrieänderungen

- Sicherstellung benachbarter Bezugsebenen

Die Impedanz sollte frühzeitig definiert und sowohl durch Berechnung als auch durch Simulation überprüft werden.

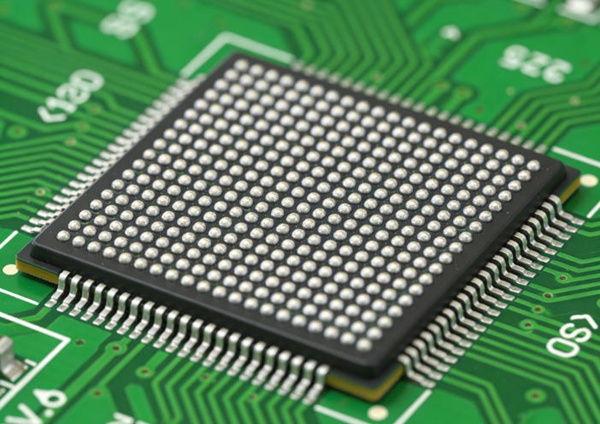

Über Auswirkungen auf die Signalintegrität

Durchkontaktierungen führen parasitäre Induktivität und Kapazität ein, wodurch Impedanzdiskontinuitäten entstehen.

Zu den bewährten Praktiken für den Umgang mit überbetrieblichen SI-Problemen gehören:

- Minimierung der Anzahl der Durchgänge in kritischen Netzen

- Reduzieren über Stummel

- Bei Bedarf Rückwärtsbohren

- Ausrichtung über die Strategie mit dem Stackup-Design

Für Hochgeschwindigkeitsschnittstellen ist häufig eine Via-Modellierung erforderlich.

Terminierungsstrategien für Hochgeschwindigkeitssignale

Eine ordnungsgemäße Terminierung trägt zur Verringerung von Reflexionen und zur Verbesserung der Signalqualität bei.

Zu den üblichen Beendigungsansätzen gehören:

- Quelle: Kündigung

- Beendigung

- Differenzielle Terminierung

Die Wahl des Anschlusses hängt von der Stärke des Treibers, der Topologie und den Schnittstellenanforderungen ab.

Die Rolle von SI-Simulation und Messung

Die Simulation spielt eine entscheidende Rolle beim modernen Hochgeschwindigkeits-Leiterplattenentwurf. SI-Simulation hilft Ingenieuren:

- Vorhersage von Reflexionen und Nebensprechen

- Impedanzprofile auswerten

- Validierung von Routing-Strategien vor der Herstellung

Messtechniken wie TDR und Augendiagrammanalyse werden zur Validierung der realen Hardware eingesetzt.

Die Simulation sollte gute Layout-Praktiken ergänzen und nicht ersetzen.

Überlegungen zur Signalintegrität und Herstellung

Fertigungsschwankungen können die Signalintegrität beeinträchtigen. Faktoren wie Leiterbahnbreitentoleranz, Variation der Dielektrizitätskonstante und Lagenregistrierung beeinflussen alle die Impedanz.

Designer sollten:

- Klare Kommunikation der Impedanzanforderungen

- Auswahl von Materialien mit kontrollierten Eigenschaften

- Verstehen von Fertigungstoleranzen

🔗 Perspektive der Herstellung:

Hochgeschwindigkeits-PCB-Design für Herstellbarkeit und Ausbeute

Zusammenfassung bewährter Praktiken für SI im Hochgeschwindigkeits-Leiterplattenentwurf

Zur Wahrung der Signalintegrität:

- Frühzeitige Erkennung von Hochgeschwindigkeitssignalen

- Definition und Kontrolle der Impedanz

- Kontinuierliche Rücklaufwege beibehalten

- Minimierung von Durchkontaktierungen und Stichleitungen

- Validierung von Entwürfen durch Simulation und Überprüfung

Die Signalintegrität wird am besten als Teil eines disziplinierten Design-Workflows und nicht als späte Korrektur behandelt.

Schlussfolgerung

Die Signalintegrität ist eine entscheidende Herausforderung bei der Entwicklung von Hochgeschwindigkeits-Leiterplatten. Durch das Verständnis des Verhaltens von Übertragungsleitungen, die Kontrolle der Impedanz und die Aufrechterhaltung geeigneter Rückleitungen können Ingenieure signalbezogene Probleme erheblich reduzieren.

Dieser Artikel bietet eine grundlegende Referenz für die Verwaltung der Signalintegrität während des gesamten Prozesses der Hochgeschwindigkeits-Leiterplattenentwicklung.

FAQ - Signalintegrität im Hochgeschwindigkeits-PCB-Design

A: Signalintegritätsprobleme werden durch Impedanzfehlanpassungen, schlechte Rückleitungen, übermäßige Durchkontaktierungen, Übersprechen und unsachgemäße Terminierung verursacht.

A: Die Anstiegszeit ist wichtiger als die Taktfrequenz. Schnelle Flanken können selbst bei relativ niedrigen Taktfrequenzen SI-Probleme verursachen.

A: Die meisten digitalen Hochgeschwindigkeitssignale profitieren von einer kontrollierten Impedanz, insbesondere wenn die Länge der Leiterbahnen im Verhältnis zur Anstiegszeit erheblich ist.

A: Das Übersprechen führt zu unerwünschtem Rauschen und Timing-Jitter, was die Augenöffnung beeinträchtigen und Funktionsstörungen verursachen kann.

A: Einige Probleme können entschärft werden, aber viele SI-Probleme erfordern Änderungen des Layouts oder des Stapels, was eine frühzeitige Designdisziplin unerlässlich macht.

A: SI-Simulationen werden für Hochgeschwindigkeitsdesigns sehr empfohlen, sind aber am effektivsten, wenn sie mit guten Layoutverfahren kombiniert werden.

A: Durchkontaktierungen führen zu parasitären Effekten und Stichleitungen, die Reflexionen verursachen können, insbesondere bei sehr hohen Datenraten.