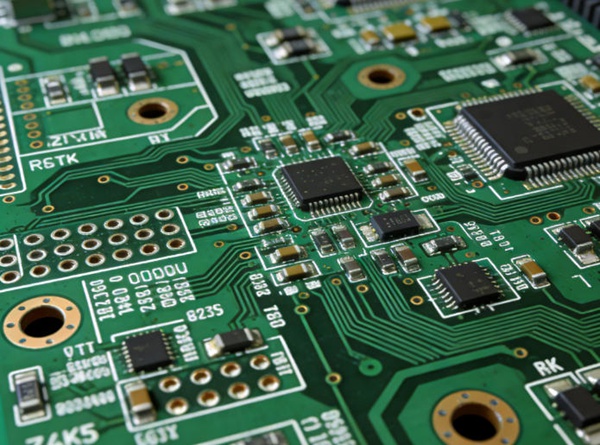

Im Bereich der Hochgeschwindigkeitselektronik ist das Leiterplattensubstrat nicht länger ein passiver Träger, sondern eine hochentwickelte dielektrische Komponente. Bei Frequenzen über 5 GHz beginnt Standard-FR-4 wie ein “Signalschwamm” zu wirken, absorbiert Energie und verzerrt Wellenfronten.

Aufbau einer zuverlässigen Hochfrequenz-Leiterplatte, Die Ingenieure müssen ein Gleichgewicht zwischen thermischer Stabilität, Produktionsausbeute und elektromagnetischer Physik finden. So geht's Hansphere nähert sich dem Material-First-Design.

1. Materialauswahl: Das Laminat auf die Anwendung abstimmen

Nicht jedes Hochgeschwindigkeitsprojekt erfordert $50/lb Material. Der Schlüssel ist die Anpassung der Dissipationsfaktor (Df) auf die Nyquist-Frequenz Ihres Signals.

Die materielle Hierarchie:

- Standardverlust (FR-4): Am besten geeignet für Steuerplatinen und digitale Geräte mit niedriger Geschwindigkeit.

- Mid-Loss (z. B. Isola FR408HR): Der “Sweet Spot” für PCIe Gen3/4 und 10G Ethernet.

- Geringer Verlust (z. B. Panasonic Megtron 6): Obligatorisch für 25 Gbps+ SerDes, KI-Beschleuniger und High-End-Server.

- Ultra-Low Loss / RF (z. B. Rogers 4350B/4003C): Wesentlich für 5G mmWave und Hochfrequenz-Leiterplatte RF-Frontends, bei denen die $Dk$-Stabilität über die Temperatur entscheidend ist.

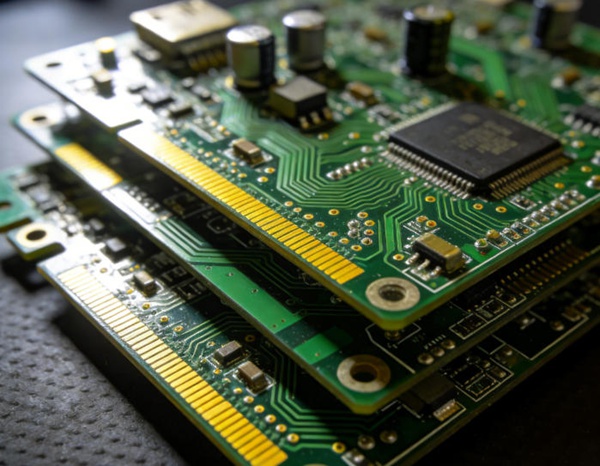

2. Strategisches Stackup-Engineering

Ein gut durchdachter Aufbau ist die erste Verteidigungslinie gegen EMI. Er bestimmt die charakteristische Impedanz und den Rückweg jedes Hochgeschwindigkeitsnetzes.

Der Rahmen “Symmetrie und Kopplung”:

- Symmetrie: Der Stapel muss physisch symmetrisch um den Kern herum angeordnet sein, um ein “Verziehen” während des PCB-Montage.

- Enge dielektrische Kopplung: Halten Sie den Abstand zwischen der Signalschicht und ihrer Bezugsebene so gering wie möglich (in der Regel 3-5 mils). Dadurch wird das elektromagnetische Feld eingegrenzt und das Übersprechen reduziert.

- Durchgängigkeit der Erdungsebene: Hochgeschwindigkeitssignale sollten niemals über einen Split in der Referenzebene laufen.

5 Schritte zur Fertigstellung eines Hochgeschwindigkeitsstapels

Ziel: Hardware-Architekten und SI-Ingenieure

Schwerpunkt: Gleichgewicht zwischen Leistung und Verarbeitbarkeit

- Schritt 1: Definieren Sie Ihre Impedanz-Ziele

Identifizieren Sie Ihre kritischen Netze (z. B. 90Ω USB, 100Ω PCIe, 50Ω Single-ended). Verwenden Sie einen Solver für elektromagnetische Felder, um die erforderlichen Leiterbahnbreiten für das von Ihnen gewählte Material zu bestimmen.

- Schritt 2: Auswahl des Kerns und Prepregs

Wählen Sie Materialien mit gleichbleibender Dk (Dielektrizitätskonstante). Für HDI-PCB, Vergewissern Sie sich, dass das Prepreg für das Laserbohren geeignet ist.

- Schritt 3: Abbilden des Signal-Rückkanals

Für jede Signalebene muss es eine angrenzende Masseebene geben. Im Jahr 2026 sind “Masse-Signal-Signal-Masse”-Konfigurationen üblich, aber sie erfordern ein sorgfältiges “orthogonales Routing” zwischen den beiden Signalebenen, um eine Breitseitenkopplung zu verhindern.

- Schritt 4: Überprüfen des Kupferfolienprofils

Bei hohen Frequenzen treibt der “Skin-Effekt” den Strom an die Kupferoberfläche. Raues Kupfer erzeugt mehr Widerstand und Verluste. Spezifizieren Sie Sehr niedriges Profil (VLP) oder Hyper-Very Low Profile (HVLP) Kupfer für Signale über 10Gbps.

- Schritt 5: Rücksprache mit Hansphere DFM

Bevor Sie den Entwurf einfrieren, senden Sie Ihren Stackup an unsere Ingenieure. Wir überprüfen, ob die Materialien vorrätig sind und ob der Harzgehalt ausreicht, um die Kupferhohlräume während der PCB-Herstellung.

3. Erweiterte Überlegungen: Thermische und hybride Stackups

- Wärmemanagement: Hochgeschwindigkeitschips werden heiß. Erwägen Sie die Verwendung Thermische Durchgänge oder sogar eine Keramische PCB Basis, wenn Ihre Anwendung HF-Verstärker mit hoher Leistung umfasst.

- Hybride Stackups: Um Kosten zu sparen, können Sie Hochgeschwindigkeitsmaterialien (wie Rogers) nur für die oberen Lagen verwenden, in denen die HF-Signale fließen, während Sie für die internen Lagen mit geringer Geschwindigkeit Standard-FR-4 verwenden.

FAQ - Hochgeschwindigkeits-PCB-Stapelung und Materialien

A: Bei hohen Geschwindigkeiten kann das Signal die Lücken im Glasfasergeflecht “sehen”, was zu Verzerrungen führt. Verwenden Sie “Spread Glass” (wie 1067 oder 1078 weave) oder verlegen Sie Ihre Leiterbahnen in einem leichten Winkel (Zickzack), um die $Dk$-Schwankungen auszugleichen.

A: FR-4 kann viele Hochgeschwindigkeitsdesigns unterstützen, aber höhere Datenraten erfordern möglicherweise Laminate mit geringem Verlust.

A: Dk bestimmt die Signalgeschwindigkeit. Ein niedriger Dk-Wert bedeutet, dass Signale schneller übertragen werden und die Leiterbahnen bei gleicher Impedanz breiter sein können, was die Skin-Effekt-Verluste reduziert.

A: Ja. Für jede Starre PCB oder Hochgeschwindigkeitsplatine liefern wir einen vollständigen TDR-Testbericht und ein Konformitätszertifikat für Ihre Stackup-Spezifikationen.

Schlussfolgerung

Stapelung und Materialauswahl sind die “unsichtbare Technik”, die digitale Hochgeschwindigkeitsübertragung ermöglicht. Durch die Wahl des richtigen Harzsystems, des Kupferprofils und der Lagenfolge schaffen Sie eine stabile Umgebung, in der Signale ohne Störungen gedeihen können.

Benötigen Sie einen Präzisionsstapler? Raten Sie nicht über die Impedanz. Hansphere's Technik-Team ist spezialisiert auf komplexe, hochschichtige Stapel mit exotischen Materialien. Kontaktieren Sie uns für eine Stackup-Überprüfung heute.