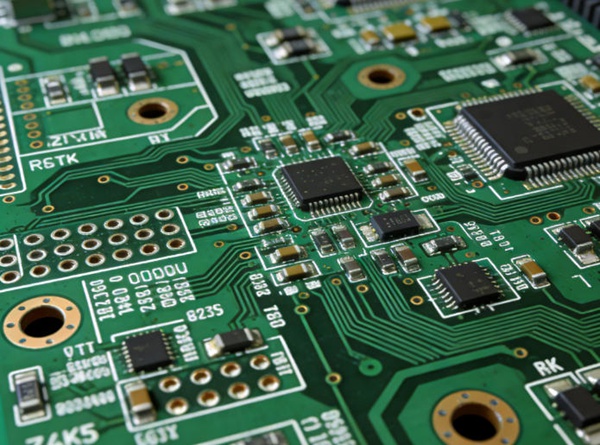

Stackup-Design und Materialauswahl bilden die physikalische Grundlage für die Leistung von Hochgeschwindigkeits-Leiterplatten. Selbst bei perfektem Routing und Signalintegritätsanalyse kann ein ungeeigneter Aufbau oder ein ungeeignetes Laminat zu Impedanzschwankungen, übermäßigen Verlusten und Fertigungsrisiken führen.

Dieser Artikel erklärt wie man einen effektiven Hochgeschwindigkeits-Leiterplattenaufbau entwirft und geeignete Materialien auswählt, Der Schwerpunkt liegt dabei auf elektrischer Leistung, Herstellbarkeit und Kostengleichgewicht.

🔗 Kernthema:

Hochgeschwindigkeits-PCB-Design: Layout, Signalintegrität, und Grundlagen des Stapelns

Warum das Stapeldesign bei Hochgeschwindigkeits-Leiterplatten wichtig ist

Bei Hochgeschwindigkeitsdesigns verhalten sich Leiterbahnen nicht mehr wie einfache Leiter. Das elektromagnetische Feld um jedes Signal interagiert direkt mit den umgebenden dielektrischen und Bezugsebenen.

Stackup-Design bestimmt:

- Charakteristische Impedanz

- Signalverlust und Dispersion

- Qualität des Rückwegs

- Crosstalk-Verhalten

- EMI-Leistung

Ein gut durchdachtes Stackup reduziert die Notwendigkeit für spätere Kompromisse beim Layout.

Typische Strukturen für Hochgeschwindigkeits-Leiterplattenstapel

Philosophie des symmetrischen Stapelns

Bei Hochgeschwindigkeits-Leiterplatten werden in der Regel symmetrische Stapel verwendet, um dies zu gewährleisten:

- Mechanische Stabilität

- Gleichmäßige Impedanzkontrolle

- Geringerer Verzug bei der Herstellung

Die Symmetrie vereinfacht auch die Herstellung und verbessert den Ertrag.

Gemeinsame Layer-Konfigurationen

Typische Hochgeschwindigkeits-Stackups sind:

- 4-lagig: Hochgeschwindigkeitsdesigns der Einstiegsklasse

- 6-8 Schichten: Die meisten gängigen digitalen Hochgeschwindigkeitskarten

- 10+ Schicht: Dichte, schnittstellenübergreifende Systeme

Kritische Signale werden in der Regel in der Nähe von soliden Bezugsebenen weitergeleitet.

Dielektrische Materialeigenschaften, die sich auf Hochgeschwindigkeitssignale auswirken

Dielektrizitätskonstante (Dk)

Dk bestimmt die Signalausbreitungsgeschwindigkeit und -impedanz. Niedrigere und stabilere Dk-Werte werden für Hochgeschwindigkeitsdesigns bevorzugt.

Die Materialbeständigkeit bei verschiedenen Frequenzen und Temperaturen ist oft wichtiger als der absolute Dk-Wert.

Dissipationsfaktor (Df)

Df steht für den dielektrischen Verlust und wirkt sich direkt auf die Signalabschwächung aus.

Bei Hochgeschwindigkeitsschnittstellen, insbesondere bei langen Kanälen, helfen Materialien mit niedrigem Df, Augenöffnungen und Timing-Spannen zu erhalten.

Glasgewebte Effekte

Glasgeflechtmuster können zu Impedanzschwankungen und Versatz führen, insbesondere bei differentiellen Paaren.

Zu den Minderungsstrategien gehören:

- Materialien aus Streuglas

- Fräsungen im Winkel zur Bindung

- Enge Impedanzkontrolle

FR-4 vs. Hochgeschwindigkeitslaminate

Standard-FR-4-Materialien sind für viele Entwürfe ausreichend, aber bei höheren Datenübertragungsraten gibt es Einschränkungen.

Hochgeschwindigkeitslaminate bieten:

- Unterer Df

- Stabilere Dk

- Verbesserte Signalintegrität

Die Wahl des Materials sollte auf Leistungsanforderungen und nicht auf Standardannahmen beruhen.

Stackup-Design für Impedanzkontrolle

Die Impedanzkontrolle beginnt auf der Ebene des Stapels.

Zu den bewährten Praktiken gehören:

- Frühzeitige Festlegung der Zielimpedanz

- Auswahl der dielektrischen Dicke auf der Grundlage von Routing-Beschränkungen

- Signalschichten in der Nähe von Bezugsebenen halten

- Vermeiden unnötiger Ebenenübergänge

Die Impedanz sollte mit den Fertigungspartnern validiert werden.

🔗 Routing-Abhängigkeit:

Best Practices für High-Speed PCB-Layout und Routing

Rückwegplanung im Stackup-Design

Kontinuierliche Rückkanäle hängen von der richtigen Platzierung der Ebene ab.

Wichtige Überlegungen:

- Dedizierte Referenzebenen für Hochgeschwindigkeitsschichten

- Minimierung der Ebenenaufteilung

- Koordinierung von Signalübergängen mit Änderungen der Bezugsebene

Stackup-Entscheidungen haben einen starken Einfluss auf das Rücklaufverhalten.

🔗 SI-Beziehung:

Signalintegrität im Hochgeschwindigkeits-PCB-Design

Herstellung und Kostenüberlegungen

Fortschrittliche Materialien und komplexe Aufbauten erhöhen die Herstellungskosten.

Designer sollten ausgleichen:

- Elektrische Leistung

- Verfügbarkeit von Material

- Ausbeute bei der Herstellung

- Gesamtkosten des Systems

Die frühzeitige Zusammenarbeit mit PCB-Herstellern reduziert Risiken und Iterationszyklen.

Zusammenfassung der Best Practices für High-Speed PCB Stackup Design

- Symmetrische Stapel verwenden

- Platzieren Sie Hochgeschwindigkeitssignale in der Nähe von festen Ebenen

- Auswahl der Materialien auf der Grundlage von Verlust und Stabilität

- Plan-Impedanz in der Stackup-Phase

- Abgleich der elektrischen Ziele mit den Fertigungszwängen

Schlussfolgerung

Stackup-Design und Materialauswahl sind die Grundlage für ein erfolgreiches High-Speed-Leiterplattendesign. Ein disziplinierter Ansatz in dieser Phase ermöglicht ein saubereres Routing, eine bessere Signalintegrität und vorhersehbare Fertigungsergebnisse.

Dieser Artikel vervollständigt das technische Grundgerüst für das physische Design von Hochgeschwindigkeits-Leiterplatten.

FAQ - Hochgeschwindigkeits-PCB-Stapelung und Materialien

A: Die erforderliche Lagenzahl hängt von der Routingdichte, den Impedanzanforderungen und den Anforderungen an die Stromverteilung ab.

A: FR-4 kann viele Hochgeschwindigkeitsdesigns unterstützen, aber höhere Datenraten erfordern möglicherweise Laminate mit geringem Verlust.

A: Symmetrische Stapelungen verbessern die mechanische Stabilität und die Fertigungssicherheit.

A: Ein höheres Df erhöht den Signalverlust und verringert die Augenöffnung und die Zeitspanne.

A: Ja. Die richtige Platzierung der Ebene und die Kontrolle des Rückwegs verringern das EMI-Risiko erheblich.

A: Materialentscheidungen sollten frühzeitig getroffen werden, idealerweise bevor die detaillierte Planung beginnt.