Irgendwann in der Hochgeschwindigkeitskonstruktion funktioniert das “Grobrouting” nicht mehr.

Sie beginnen zu sehen:

- Reflexionen

- Signalverzerrung

- instabile Verbindungen

In diesem Fall ist eine Impedanzkontrolle erforderlich.

Die meisten Entwürfe zielen darauf ab:

- 50Ω (single-ended)

- 100Ω differentiell (gepaarte Signale)

Um dieses Ziel zu erreichen, kommt es nicht nur auf die Leiterbahnbreite an, sondern auf eine Kombination aus Stapelung, Materialien und Fertigungstoleranzen.

Was ist kontrollierte Impedanz?

Kontrollierte Impedanz bedeutet, dass die Leiterbahnen auf der Leiterplatte so gestaltet sind, dass ihre charakteristische Impedanz innerhalb einer bestimmten Toleranz liegt (z. B. 50Ω ±10%).

Es kommt darauf an:

- Leiterbahnbreite

- Spurendicke

- dielektrische Dicke

- Dielektrizitätskonstante (Er)

- Bezugsebene

Ändert sich einer dieser Werte, ändert sich die Impedanz.

Hintergrund zu Er: FR4 Dielektrizitätskonstante (Er) vs. Frequenz erklärt

Warum 50Ω und 100Ω?

Diese Werte sind nicht zufällig.

- 50Ω ist ein gängiger Standard für unsymmetrische HF- und Hochgeschwindigkeitssignale

- 100Ω differentiell wird häufig für Schnittstellen wie LVDS, USB, Ethernet

Sie stellen ein Gleichgewicht zwischen:

- Signalverlust

- Leistungsaufnahme

- Herstellbarkeit

Gemeinsame Strukturen von Übertragungsleitungen

Die Impedanz hängt stark von der Stapelung ab.

Microstrip (äußere Schicht)

- Spur auf äußerer Schicht

- Bezugsebene unten

Vorteile:

- leicht zu leiten

- zugänglich

Nachteile:

- mehr EMI

- empfindlicher gegenüber der Umwelt

Stripline (innere Schicht)

- Leiterbahn zwischen zwei Bezugsebenen

Vorteile:

- bessere Abschirmung

- geringere EMI

- stabilere Impedanz

Nachteile:

- erschwerter Zugang

- strengere Fertigungskontrolle

Stackup-Grundlagen: FR4 PCB Stackup Design Leitfaden

Schlüsselfaktoren, die die Impedanz beeinflussen

1. Leiterbahnbreite

Breitere Leiterbahn → niedrigere Impedanz

Schmalere Leiterbahn → höhere Impedanz

2. Dielektrische Dicke

Größerer Abstand zur Ebene → höhere Impedanz

3. Dielektrizitätskonstante (Er)

Höhere Er → niedrigere Impedanz

4. Dicke des Kupfers

Dickeres Kupfer senkt die Impedanz leicht

5. Qualität der Bezugsebene

Für eine stabile Impedanz ist eine durchgehende Ebene erforderlich.

Details zum Rückweg: PCB-Rückleitung und Massefläche im Hochgeschwindigkeitsdesign

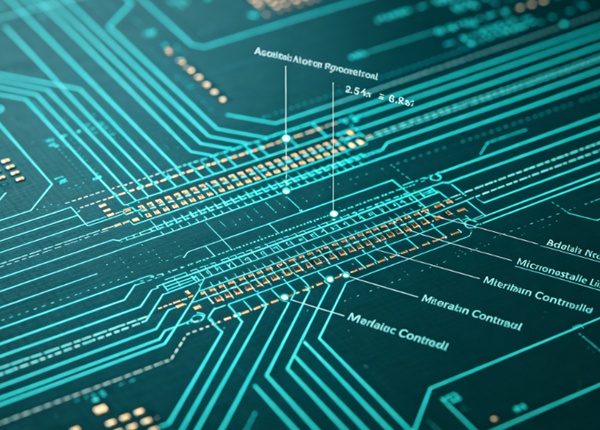

50Ω vs. 100Ω Differenzial (Schnellvergleich)

| Parameter | 50Ω Einseitig endend | 100Ω Differenzial |

|---|---|---|

| Signalart | einzelne Zeile | gepaarte Linien |

| Empfindlichkeit | mäßig | höher |

| Routing-Komplexität | unter | höher |

| Störimmunität | unter | höher |

Differentialpaare beruhen auf einer engen Kopplung zwischen den beiden Leiterbahnen.

Wie man eine kontrollierte Impedanz erreicht

Dies ist der Punkt, an dem Entwürfe erfolgreich sind oder scheitern.

- 1. Beginnen Sie mit Stackup (nicht Routing)

Definieren Sie:

.layer Struktur

.dielektrische Dicke

.material type

...bevor Sie etwas verlegen.

Wenn der Stackup falsch ist, lässt sich das durch Trace-Tuning nicht beheben. - 2. Verwendung von Impedanzrechnern oder Feldlösern

Die Werkzeuge schätzen die Geometrie der Spur auf der Grundlage:

.Zielimpedanz

.material properties

Aber denken Sie daran: Werkzeuge sind Näherungswerte. - 3. Arbeiten Sie frühzeitig mit Ihrem Leiterplattenhersteller zusammen

Dieser Schritt wird oft übersprungen und führt später zu Problemen.

Hersteller bieten:

.aktuelle Laminatdaten

.erreichbare Toleranzen

.Impedanztabellen

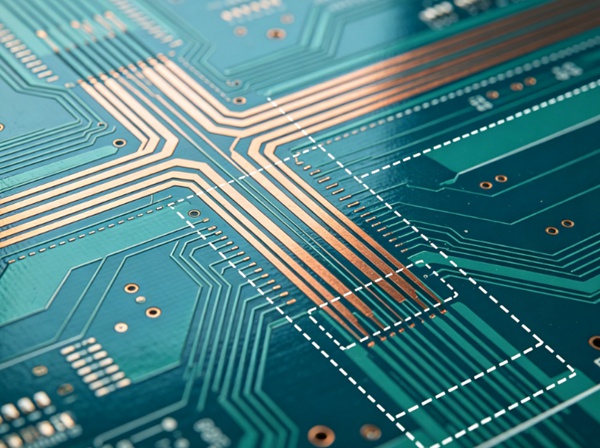

Sie können den Stackup anpassen, um Ihr Ziel zu treffen. - 4. Geometrie des Steuerdifferenzialpaares

Für 100Ω Differential:

. die Abstände zwischen den Leiterbahnen sind ebenso wichtig wie die Breite

. engerer Abstand → geringere Differenzimpedanz

Auch behalten:

. gleiche Länge

. einheitliche Abstände

. minimale Schräglage

Überschneidungen: PCB-Nebensprechen erklärt (Nahnebensprechen vs. Fernnebensprechen) - 5. Kontinuierliche Bezugsebenen beibehalten

Vermeiden:

. Flugzeug spaltet sich

. Verlegung über Hohlräume

Diese unterbrechen die Impedanzkontinuität. - 6. Berücksichtigung von Fertigungstoleranzen

Echte Bretter variieren.

Typische Toleranz:

. ±5% bis ±10% Impedanz

Gestalten Sie also die Margen entsprechend.

Häufige Fehler

Diese tauchen häufig auf:

- Definition der Impedanz nach dem Routing

- Vernachlässigung der Prepreg-Schwankungen

- die sich nur auf allgemeine Er-Werte stützen

- keine Rückmeldung vom Hersteller

- Unterbrechung von Rückleitungen durch Durchkontaktierungen oder Spaltungen

Überprüfung der Impedanz

Man kann nicht einfach “dem Design vertrauen”.

1. Simulation

Feldlöser schätzen Impedanz und Verlust.

2. Fabrikations-Testcoupons

Die Hersteller bauen Impedanzteststrukturen in die Platte ein.

3. Messung

- TDR (Zeitbereichsreflektometrie)

- Impedanzmessgeräte

Diese bestätigen die tatsächlichen Ergebnisse.

Praktische Gestaltungshinweise

Aus realen Projekten:

- Stackup-Entscheidungen sind wichtiger als Trace-Tweaks

- innere Schichten sind stabiler als äußere Schichten

- kleine Abstandsfehler können die differentielle Impedanz unterbrechen

- Kommunikation mit der PCB-Fertigung spart Zeit

Schlussfolgerung

Das Design mit kontrollierter Impedanz ist eine Kombination aus Geometrie, Materialien und Fertigungskontrolle.

50Ω- und 100Ω-Ziele sind erreichbar, aber nur, wenn Stapelung, Routing und Fertigung aufeinander abgestimmt sind. Je früher die Impedanz im Entwurfsprozess berücksichtigt wird, desto einfacher ist es, die Leistungsanforderungen zu erfüllen.

FAQ

A: Es bedeutet, Leiterbahnen so zu gestalten, dass ein bestimmter Impedanzwert innerhalb der Toleranz gehalten wird.

A: Es bietet ein Gleichgewicht zwischen Signalintegrität und Herstellbarkeit für viele Anwendungen.

A: Weil zwei gekoppelte Leiterbahnen zusammen eine Standard-Differentialimpedanz ergeben, die in vielen Schnittstellen verwendet wird.

A: Nicht einfach. In der Regel sind dafür Änderungen an der Stapelung oder Geometrie erforderlich.

A: Typischerweise innerhalb von ±5% bis ±10%, je nach Fertigungsmöglichkeiten.